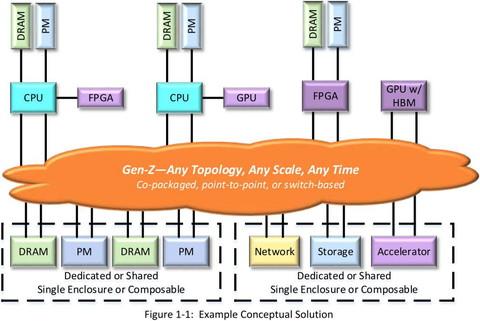

2回続けてOpenCAPIの話をしたところだが、今回はGen-Zに話を戻したい。もともとGen-ZがDRAMの接続を当初から考慮していたのは、こちらの記事でも紹介した通りで、実際2016年には"Gen-Z+DDR:A winning combination"なるホワイトペーパーも出されており、この中で複数のDDRメモリをGen-Z経由で接続するというアイディアが示されてる。

Gen-Zの“先に”メモリコントローラーを置くというアイディア。実はGen-Zではなく独自のInfinityFabricではあるが、AMDは第3世代のRyzenでこれを実装しているので、これはこれでアリであるSCMやフラッシュまで混載する場合は、専用のコントローラーをさらに設けましょうという話前回紹介した「OpenCAPI 3.1」のOMI(Open Memory Interface)との違いは、メモリコントローラーがInterconnectの手前、つまりプロセッサー側にあるのか、先にある(つまりDRAM側)のかという点だ。OMIではプロセッサー側に、Gen-ZではDRAM側にそれぞれ置かれることになる。

どちらがいいかは実装次第となるが、OpenCAPIはまだ3.0の段階で、この時点ではそもそもDRAMを扱えなかった。その関係で、OMIのような過渡的なソリューションに頼らざるを得ない状況であり、そうなるとメモリコントローラーはプロセッサー側に置かざるを得なかった、ということがある。

対するGen-Zでは、そもそもInfiniBandを使ったHPC向けInterconnectの段階で、メモリ共有をすでに実現していた。例えばホストAとホストBをInfiniBandで接続する場合に、ノードAとノードBのそれぞれに共有メモリ領域を設け、片方にデータが書き込まれたら即座に相手側にもそれを反映するというのがその仕組みだ。

MPIでこれを利用すれば、複数ノード間でプログラムの同期が取れるわけだ。InfiniBandはこの段階で、プロセッサーの先にメモリコントローラーを置く構成をサポートしているわけで、Gen-Zでも当然これを引き継ぐこととなる。

そんなわけで、CAPI 3.1とはまた違った方式ではあるが、Gen-Zでも同様のことは当然可能だ。コネクタ類も当初からDRAM接続に対応しており(というかOpenCAPIとは異なり、そもそもインターフェースが共通化されているので、別のコネクタを定義する必要がない)、理論上は問題なく利用可能だ。